Библиотека 22

Визуальные java-апплеты

Прекрасно иллюстрируют электрические процессы.

Опубликованы в flv, только для ознакомления

Выделенные светло-синим цветом элементы являются активными.

С них снимаются основные электрические характеристики

(осциллограммы, графики,и.т.д) показанные внизу апплета.

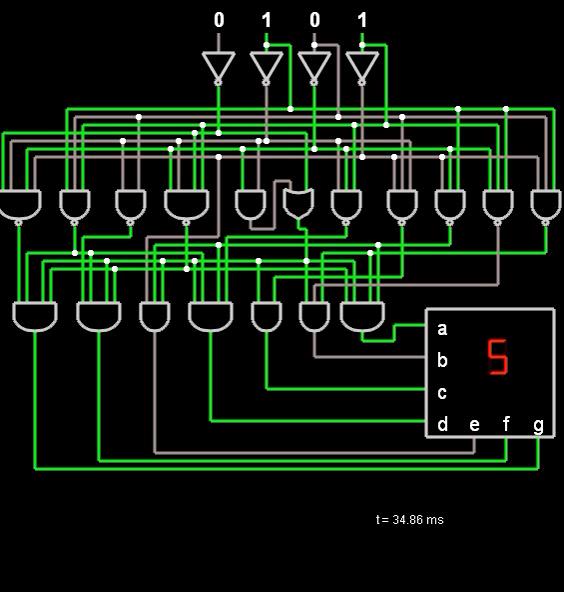

7-сегментный индикатор Декодер. Схема вводит 4-значное двоичное число и выводит десятичную цифру от 0 до 9 с помощью 7-сегментного светодиодного дисплея. Если число больше, чем 9, то дисплей остается пустым.

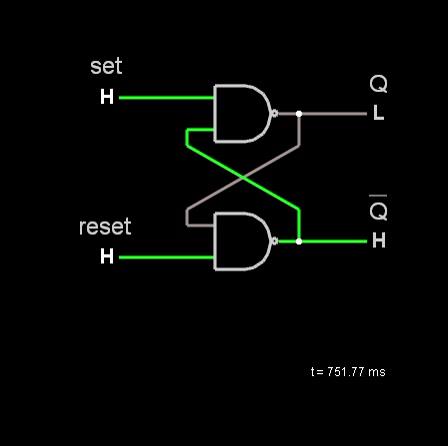

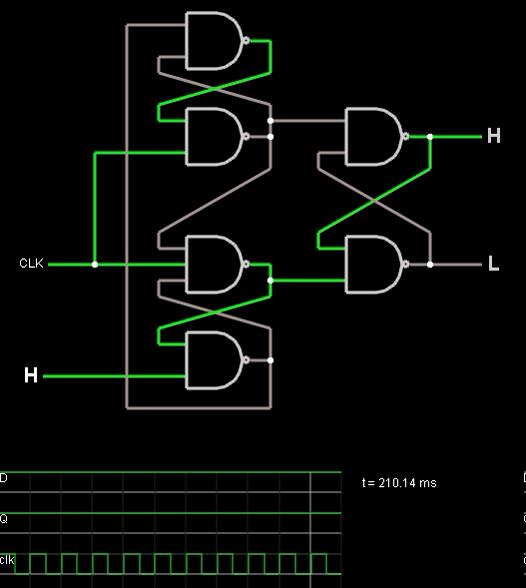

RS-триггер. Схема флип-флоп или защелки, которая хранит один бит памяти. В нулевой момент времени, когда ни на один вход (R и S) не подана логическая единица, прямой выход Q=0, соответственно, инверсный =1. Если на вход S подать напряжение, уровень которого будет соответствовать единице, то выход Q скачкообразно изменит свое значение на 1, а на 0. Это произойдет запись информации. Если убрать единицу с “Set”, тогда выходы не изменят свое состояние, останутся такими, какими были – проявление свойства памяти. При подаче положительного сигнала на вход сброса, то есть R=1, инверсный выход резко станет равен 1, а прямой Q – 0. В работе RS-триггера есть недостаток: существует запрещенная комбинация. Нельзя одновременно подавать единичные сигналы на оба входа, нормальная работа триггера в этом случае невозможна.

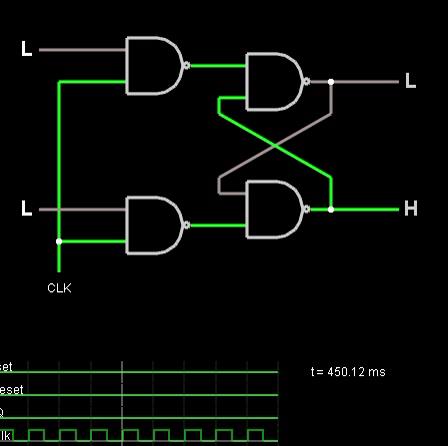

Схема с тактовой установкой сброса RS-триггера. Выход только меняется, когда входной тактовый сигнал высокий.

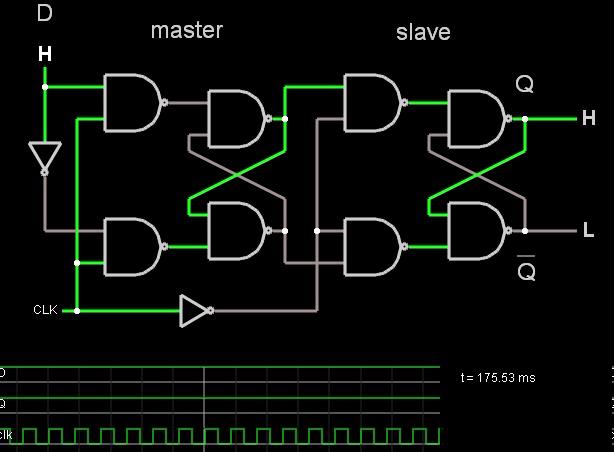

MS-триггер. MS-триггер является синхронным двухступенчатым триггером со статическим управлением. Схемотехнически он выполняется на двух триггерах: M(master - основной) и S(slave - вспомогательный). М-триггер воспринимает входную информацию, а S-триггер фиксирует состояние триггера в целом. При этом оба триггера могут быть однотипными, например RS- или D-триггеры, или различными. Управляющая связь между М-триггером и S-триггером осуществляется двумя синхро сериями, либо посредством запрещающего инвертора.

Триггер, тактируемый перепадом напряжения тактируемый фронтами импульсов. На входы логического элемента или устройства сигналы не всегда поступают одновременно, так как перед этим они могут проходить через разное число элементов с различной задержкой. В результате в течение некоторого времени на входах может создаться непредвиденная ситуация: новые значения одних сигналов могут сочетаться с предыдущими значениями, что может привести к ложному срабатыванию. Такую ситуацию можно устранить временным стробированием, когда на элемент, кроме информационных сигналов, подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы заведомо успевают установиться на входах.Тактируемый триггер, кроме информационных входов, имеет синхронизирующий (тактирующий, тактовый) вход; сигналы на информационных входах воздействуют на такой триггер только с поступлением сигнала на синхронизирующий вход.

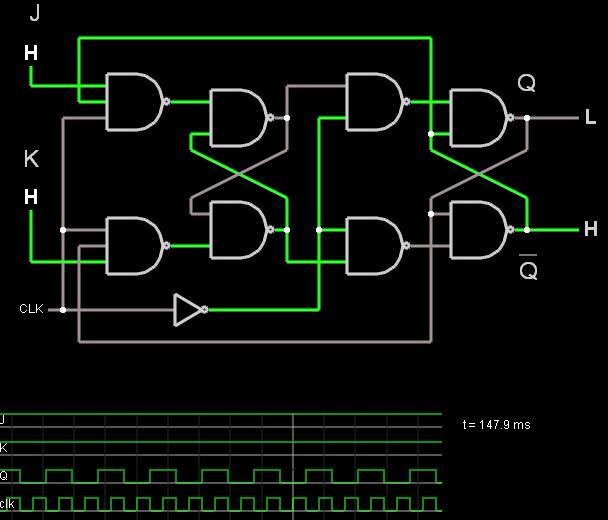

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J аналогичен входу S у RS-триггера. Вход K аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем.

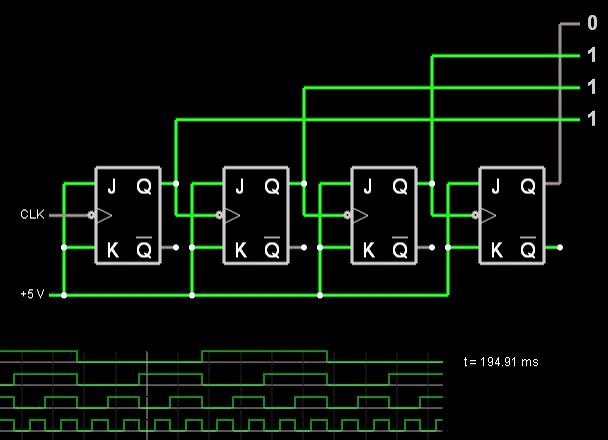

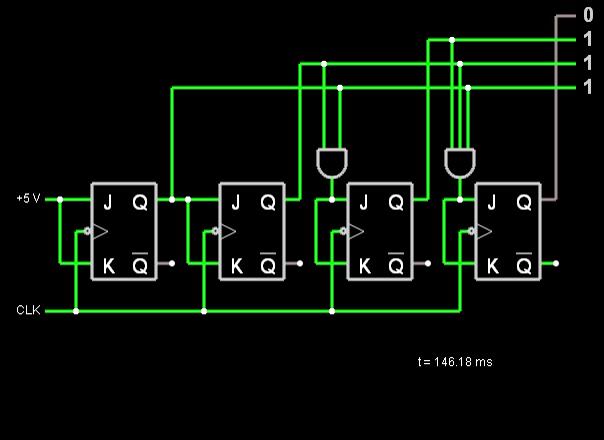

4-разрядный счетчик пульсаций. Последовательные данные и их дополнения подаются на JK входы триггера А. Остальные триггеры соединены каскадно, то есть выходы одного подсоединены к выходам следующего. Переключатели всех триггеров соединены вместе, и по этой линии подаются тактовые импульсы. Поскольку все триггеры переключаются одновременно - цепь является синхронной. Кроме того, входы очистки каждого триггера соединены вместе и образуют линию сброса. Данные, поданные на вход, сдвигаются триггерами на один разряд по каждому тактовому импульсу. Например, если на вход сдвигового регистра подано двоичное число 1011, и подан сдвиговый импульс, то число, записанное в сдвиговом регистре, выдвигается на один разряд и теряется, тогда как новое число сдвигается на один разряд.

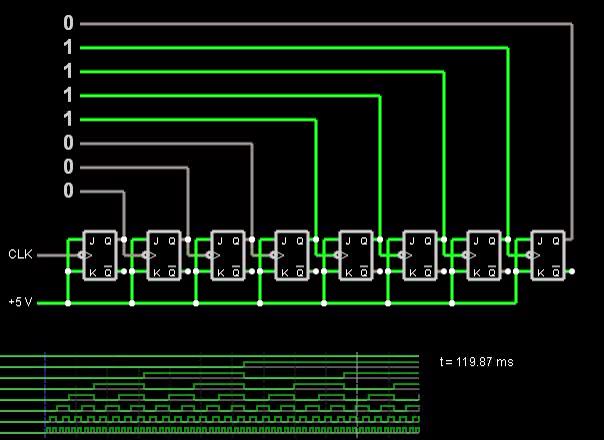

8-разрядный счетчик пульсаций. Работает аналогично как 4-разрядный счетчик пульсаций.

4-разрядный синхронный счетчик. У первого триггера (младший значащий разряд A) J = К = 1, так что он изменяет свое состояние с каждым тактовым импульсом. У второго триггера (В) J = К = А, поэтому он переключается только в том случае, когда А = 1. Третий триггер (С) может переключаться только тогда, когда и А и В равны 1, в то время как четвертому триггеру D для переключения необходимо равенство 1 С, В и А. Следуя таблице переходов, описывающей эту процедуру, видим, что схема работает аналогично асинхронному счетчику, за исключением того, что все триггеры переключаются вместе, все тактовые входы объединены в один вход CP вместо того, чтобы по отдельности быть подключенными к выходам предыдущих триггеров.

|

|