Как известно, основная операция в цифровых вычислительных машинах - сложение. Все другие арифметические операции - вычитание, умножение, деление - сводятся к сложению. Операция сложения двоичных чисел производится с использованием сумматоров, полусумматоров и сумматоров по модулю 2.

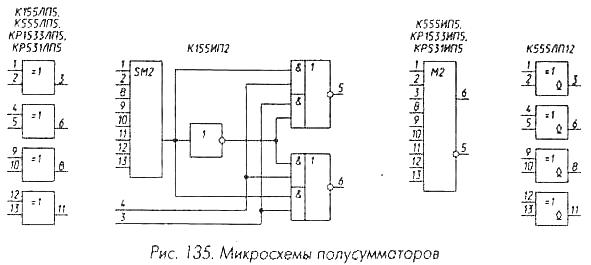

Микросхема ЛП5 (рис. 135) - четыре независимых сумматора по модулю 2, каждый из которых работает следующим образом. Если на обоих входах элемента, например 1 и 2, лог. 0 - на выходе 3 лог. 0. Если на одном из входов лог. 0, на другом лог. 1, на выходе лог. 1, если на обоих входах лог. 1 - на выходе лог. 0.

В состав микросхемы К155ИП2 (рис. 135) входят восьмивходовый сумматор по модулю 2, обозначенный SM2, инвертор и два логических элемента И-ИЛИ-НЕ. Восьмивходовый сумматор по модулю 2 работает аналогично двувходовому: если на его входах четное число сигналов с уровнем лог. 1, на выходе лог. 0, если число единиц на входах нечетное, на выходе лог. 1. Остальные элементы позволяют объединять микросхемы между собой для увеличения числа входов. При подаче лог. 1 на вход 3, лог. 0 на вход 4, уровень на выходе 5 будет соответствовать выходному уровню сумматора SM2, на выходе 6 -его инверсии. Если уровни на входах 3 и 4 изменить на противоположные, уровни на выходах 5 и 6 изменятся на противоположные.

Микросхема К555ИП5 (рис. 135) - девятивходовый сумматор по модулю 2. Выходной сигнал на прямом выходе 6 соответствует лог. 1 при нечетном числе лог. 1 на входах микросхемы и равен лог. 0 в противном случае. Сигнал на инверсном выходе всегда противофазен сигналу на прямом.

Микросхему К555ИП5, так же как К155ИП2, можно использовать для формирования разряда контроля четности при передаче данных

или при записи в память или на какие-либо носители данных, а также при проверке данных, снабженных контрольным разрядом, при их приеме или считывании из памяти или с носителей данных.

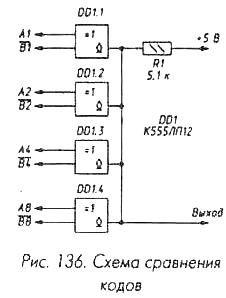

Микросхема К555ЛП12 (рис. 135) - четыре двухвходовых сумматора по модулю 2 с открытым коллектором. Логика работы элементов такая же, как и у элементов микросхем ЛП5. Возможность объединения выходов элементов позволяет использовать микросхему для сравнения кодов чисел на равенство (рис. 136). Одно из сравниваемых чисел должно быть представлено прямым кодом, другое - инвертированным. При равенстве чисел на входах каждого из элементов будут неодинаковые логические уровни, на выходах элементов и, следовательно, на их общем выходе - лог. 1. Если хотя бы в од

ном разряде коды будут различаться, сигналы на входах соответствующего элемента совпадут и на объединенном выходе сформируется лог. 0.

Напомним основные свойства двоичных сумматоров. Каждый разряд двоичного сумматора (его также называют полным сумматором) имеет три входа (А и В - для слагаемых, С - сигнала переноса от предыдущего разряда) и два выхода (S - суммы и Р - сигнала переноса в следующий разряд). Работа сумматора иллюстрируется табл. 6. Входы А, В, С, вообще говоря, равноправны. Сигнал суммы S принимает значение лог. 1 при нечетном числе единиц на входах А, В и С и лог. 0 при четном, как и в рассмотренных выше полусумматорах. Сигнал переноса Р равен лог. 1 при числе единиц на входах, равном 2 или 3. Интересным свойством табл. 6 является ее симметрия: замена 0 на 1, и наоборот не нарушает ее истинности. Это свойство используется Для упрощения схем сумматоров.

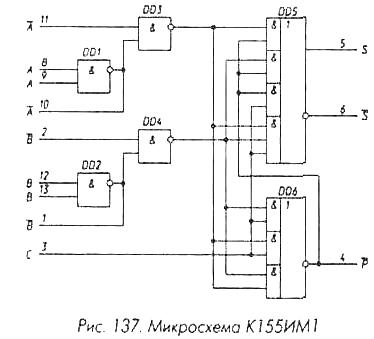

Микросхемы К155ИМ1, К155ИМ2 и К155ИМЗ - соответственно одноразрядный, двухразрядный и четырехразрядный полные сумматоры. На рис. 137 приведена схема микросхемы К155ИМ1. Ее основу

Таблица 6

|

Входы |

Выходы |

Входы |

Выходы |

||||||

|

А |

B |

C |

S |

Р |

А |

B |

C |

S |

Р |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

составляют два многовходовых элемента И-ИЛИ-НЕ. Сигнал переноса (инверсный) формируется на выходе Р, если хотя бы на двух входах сумматора имеется уровень лог. 1. При А=В=1 включается нижний элемент И DD6, при А=С=1 включается средний элемент DD6, при В=С=1 включается верхний элемент. Сигнал переноса формируется, конечно, и при А=В=С=1. Сигнал суммы формируется в случае, если А=В=С=1и включается нижний логический элемент И DD5. Сигнал суммы формируется также и в том случае, когда есть хотя бы одна единица на входах А, В, С и нет сигнала на выходе переноса (Р=1, включается один из трех верхних элементов И DD5). Поскольку сигнал переноса формируется в том случае, когда среди входных сигналов число единиц две или три, второй случай формирования сигнала суммы соответствует одной и только одной единице среди входных сигналов. Если на всех входах сигналы отсутствуют (А=B= С=0), выходные сигналы также отсутствуют: S = 0, Pинв=1 (Р=0).

Входные сигналы А и В могут быть поданы не только в прямом коде (входы 8 и 9 для А, 12 и 13 для В), но и в инверсном (входы 11 для А и 2 для В). При использовании инверсных входных сигналов входы 8,9,12 и 13 следует соединить с общим проводом, а при использовании прямых сигналов - попарно соединить выводы 10 и 11,1 и 2.

Элементы DD1 и DD2 микросхемы имеют открытый коллекторный выход, поэтому выводы 10 и 1 можно использовать или как выходы элементов DD1 и DD2, или как входы, превращающие элементы DD1 и DD2 типа И-НЕ в элементы И-ИЛИ-НЕ подключением к этим выводам выходов микросхемы К155ЛА8. В любом случае использования выводов 10 и 1 между ними и полюсом питания необходимо включать резисторы сопротивлением 1...2 кОм.

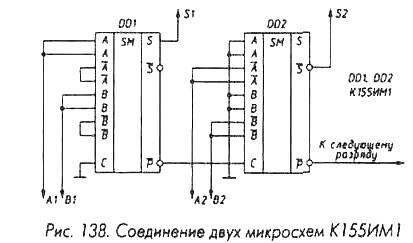

При соединении микросхем К155ИМ1 в многоразрядный сумматор (рис. 138) используется описанное выше свойство симметрии полного сумматора относительно замены входных и выходных сигналов инверсными. В первом разряде входные сигналы подаются на прямые входы DD1, выходной сигнал суммы снимается с прямого выхода S, сигнал переноса - с единственного (инверсного) выхода P. На второй разряд сумматора входные сигналы А и В подаются на инверсные входы, на прямой вход С подается инверсный сигнал переноса с первого разряда, выходной прямой сигнал суммы формируется на инверсном выходе S, выходной прямой сигнал переноса - на инверсном выходе Pинв. Третий разряд сумматора работает так же, как и первый, четвертый - как второй, и т. д. Такое чередование режима работы одноразрядных сумматоров обеспечивает минимальную задержку распространения сигнала в самой длинной цепи - в цепи формирования сигнала переноса.

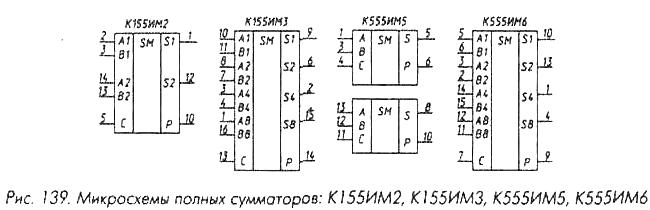

Микросхема К155ИМ2 (рис. 139) представляет собой объединение двух микросхем К155ИМ1, соединенных в соответствии с рис. 138 с исключенными неиспользуемыми инверторами. Микросхема К155ИМЗ (рис. 139) соответствует двум микросхемам К155ИМ2, в которых выход переноса первой микросхемы соединен с входом С второй.

Микросхема К555ИМ5 - два полных одноразрядных сумматора (рис. 139), каждый из которых имеет три входа (А и В - для подачи двух слагаемых, С - переноса от предыдущего разряда) и два выхода (S - суммы, Р - переноса).

Микросхема К555ИМ6 (рис. 139) - полный четырехразрядный двоичный сумматор. Ее логика работы соответствует логике работы микросхемы К555ИМЗ - на входы А1 - А8 подается код одного из суммируемых чисел (А1 - младший разряд, А8 - старший), на входы В1-В8 - код второго числа, на вход С - перенос от предыдущей микросхемы. Код суммы формируется на выходах S1 - S8, перенос - на выходе Р. У микросхемы, суммирующей младшие разряды многоразрядных двоичных чисел, вход С следует соединить с общим проводом.

Микросхема К555СП1 (рис. 140) служит для сравнения кодов двух четырехразрядных двоичных или двух одноразрядных двоично-десятичных чисел. Коды сравниваемых чисел подают на входы А1 - А8 и В1 - В8. Если число, код которого подан на входы А1 - А8, больше числа, код которого подан на входы В1-В8, на выходе > микросхемы появляется лог. 1, на выходах = и < - лог. 0. Если код числа А меньше кода числа В, лог. 1 появляется на выходе <, на выходах = и > - лог. 0. Если коды, поданные на входы А и В, равны, микросхема передает на свои выходы сигналы со входов >, < и =, если на этих входах только одна лог. 1.

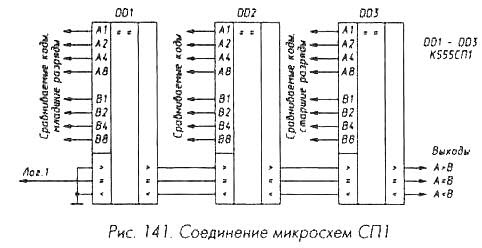

На рис. 141 показано соединение микросхем К555СП1 в многоразрядное устройство сравнения.

Микросхемы К555СП1 могут найти применение в устройствах определения равенства или знака разности двух чисел, в устройствах автопоиска записей в магнитофонах, в таймерах и других случаях.

Если необходимо только определить, равны или не равны сравниваемые коды, входы > и < всех микросхем можно не соединять

с выходами предыдущих микросхем, а соединить с общим проводом, как это сделано со входами микросхемы DD1.

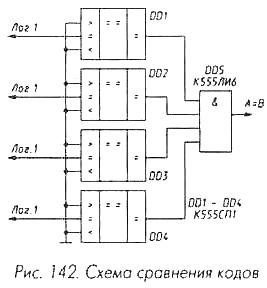

Если необходимо максимальное быстродействие устройства определения равенства двух чисел, следует подать на микросхемы К555СП1 коды сравниваемых чисел так, как показано на рис. 141, сигналы на управляющие входы - как показано на рис. 142, выходы объединить с помощью многовходового элемента И или И-НЕ.

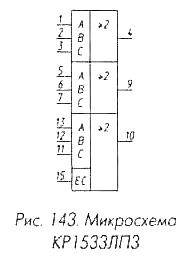

Микросхема КР1533ЛПЗ - три мажоритарных клапана (рис. 143), имеющих дополнительный вход управления ЕС.

При лог. 0 на входе ЕС выходной сигнал мажоритарного клапана соответствует входным сигналам на большинстве входов А, В, С, то есть если лог. 1 на двух или на трех входах, на выходе лог. 1, если лог. 1 только на одном входе или на всех входах мажоритарного клапана лог. 0, на выходе - лог. 0.

При подаче на дополнительный вход ЕС лог. 1 на выход клапана проходит сигнал с входа С независимо от сигналов на других входах.

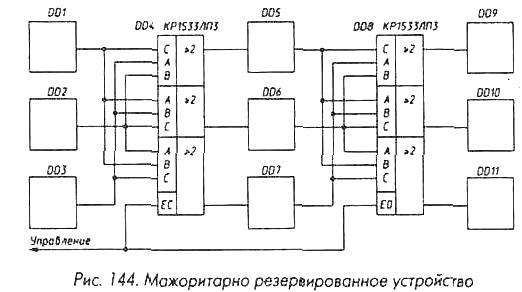

Основное применение мажоритарных клапанов - использование в системах мажоритарного

резервирования. Идея мажоритарного резервирования - построение устройства, от которого требуется высокая надежность, в виде трех идентичных устройств, выходные сигналы которых объединяются с помощью мажоритарных клапанов. В этом случае выход из строя одного из устройств не приведет к появлению неправильных выходных сигналов мажоритарных клапанов, так как их выходные сигналы будут определяться сигналами двух исправных устройств. Если каждое из устройств разбить на несколько блоков, между которыми встроить мажоритарные клапаны, можно еще более повысить надежность устройства в целом. На рис. 144 в качестве примера приведена схема сложного устройства, не выходящего из строя при выходе из строя любого из его блоков, или даже двух, например DD1 и DD7. Если мажоритарные клапаны установить и на выходы DD9 - DD11, любой из этих блоков также может выйти из строя, что не приведет к выходу из строя устройства в целом.

Наличие входа «Управление» позволяет проверить исправность всех блоков и спрогнозировать надежность устройства. Если на этот вход подать лог. 1, мажоритарное резервирование действовать не будет, устройство разделится на три независимых канала: DD1-DD5-DD9, DD2-DD6-DD10, DD3-DD7-DD11, и при контроле выходных сигналов любая неисправность будет обнаружена.

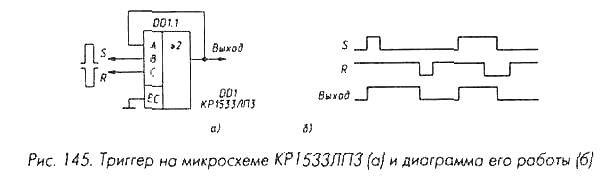

В радиолюбительской практике микросхема КР1533ЛПЗ может найти применение в качестве двухвходовых элементов И при подсоединении третьего входа к общему проводу, в качестве двухвходового элемента ИЛИ при подсоединении третьего входа к плюсу питания. Интересный вариант использования мажоритарного клапана в качестве RS-триггера приведен на рис. 145 (а). Нормально на входе S должен быть лог. 0, на входе R - лог 1. В этом случае триггер может находиться в одном из двух устойчивых состояний. При подаче на вход S лог. 1, по крайней мере, на двух входах мажоритарного клапана будет лог. 1, на выходе появится лог. 1, она сохраняется при восстановлении на входе S лог. 0 (рис. 145, б). Аналогично произойдет переключение триггера в состояние 0 при подаче лог. 0 на вход R. При строго одновременной подаче лог. 1 на вход S и лог. 0 на вход R триггер должен сохранить исходное состояние, но лучше такого варианта подачи сигналов не допускать.